什么是EMC设计评审?

大部分硬件工程师是用来做功能设计评论他们的电路板和系统制造前按下“go”按钮。和我一起工作的工程团队,这种设计评审通常已经站在一个会议室表的形式用红笔和最大的打印输出的图表,我们可以让我们的手。它也可以由一个人在电脑之间的交叉探索使图表和布局(如果你的老板是足以让许可!)。我们筛选了设计、销销和连接器,连接器,决心找到一个意外逆转接口或符号不正确固定。你知道有一个好的机会,你前面的图表包含一个隐藏的错误,有可能把你的高端线路板变成一个昂贵的啤酒的过山车,或花费你大量的返工时间至少!

公司在球标准化这种审查过程到一个正在运行的基于清单的过程,通过在每一个设计和验证。通过这样做,他们增加的可靠性评估和减少的可能性主要问题通过裂缝下滑。

令人惊讶的是,很少有公司,多年来我一直参与迁移这一重要过程分为EMC的世界。在同样的方式,功能设计评审可以捕获许多设计错误,一个坚实的EMC设计评审可以捕获许多已知的设计实践排放和免疫性能差。它可以意味着你的产品的差别通过或失败EMC测试实验室。

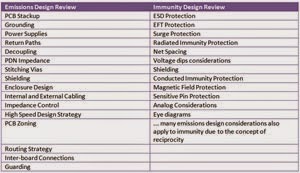

良好的EMC设计审查应包括整个产品设计的许多方面。顶级的设计审查应包括主题,如:

EMC功能规范

我喜欢把EMC测试作为一个完全独立的功能规范。有一组特定的通过/失败标准你的产品必须满足,否则你不能卖掉它。就是这么简单。没有明确规范的测试你的产品将会受到EMC实验室,你缺少一个功能规范,真正应该考虑在项目的设计阶段。你不会的梦想设计一个产品没有明确的特性集被提供给最终客户好吗?EMC测试只是一种不同的特性集,您的设计需要包含。没有EMC功能规格,你要离开在EMC实验室通过或失败的机会。这是不是巧合,据天祥集团(世界上最大的实验室组织之一),全球EMC第一次通过率只有50%吗?

在这篇文章中我将给什么是EMC设计评审的概述以及如何做一个在你的下一个产品。

为什么要做EMC设计评审?

EMC失败可以很容易地成本贵公司在有形的几千美元费用如招聘顾问,租调试设备、修订/制造设计和支付当时提取。许多公司更大的担忧是EMC的延迟市场可能会导致失败。因为EMC需要批准才能合法出售你的产品,市场的失败可以引入一个延迟几天到几周。最长的推迟上市,我遇到由于EMC失败是大约4个月公司真正难以解决的问题通过几个设计迭代,但我也不会感到惊讶,如果再延迟存在。

会计师普遍认同,推迟市场将任何给定产品的峰值销量减少几个百分点,取决于你的产品的性质,可以减少整体销售窗口的长度。对于许多大中型硬件公司,1个月延迟可以很容易地导致总体收入减少为特定产品在其寿命大于100万美元。突然,考虑EMC在设计周期的早期,看起来不像一个坏主意。

最后,做一个健壮的EMC设计评审可以增加产品的性能,因此减少客户的回报。例如,一个公司的产品相对贫穷的免疫保护可能会得到很多回报由于静电放电损伤来自最终用户的手指按按钮时的产品。或者该产品将用于相对嘈杂的电磁环境和设备的功能的影响在某些方面如射频性能退化或测量精度。良好的EMC设计可以减少这类问题。

公司有幸有EMC专家人员可能没有实现一个健壮的EMC设计评审(然而),但是知识锁在专家的头可能已经引入一个特别审查。我注意到的是,设计工程师有重要经验与EMC测试倾向于使用他们的记忆的EMC失效模式,以避免将来再次遇到相同的问题。例如,当他们制定一个电路板(或指导一个绘图员),他们可能还记得前一个产品设计失败的辐射排放由于过量的噪音在外部布线。工程师把他们实现的任何设计改进减少布线上的噪声,这种方法适用于所有的设计在未来。他们实际上做的是建立一套设计规则,他们遵循连续每个设计。当他们经历更多EMC问题和解决这些问题,他们将这些规则添加到现有的精神。

标准化这些规则到正式设计审查程序重复执行一个健壮的EMC设计评审的关键。福特和捷豹等公司面临一些艰难的EMC的挑战(汽车)实现健壮的EMC设计评论。我相信每个人都可以受益于这种方法。形式化的EMC设计审查的一个巨大的好处是,它可以由一个相对初级工程师没有太多经验的EMC设计遵从性。这是因为它更容易检查一个特定的设计规则已正确实现比做全面的EMC训练和理解为什么一个规则从物理的角度看是有道理的。没有经验丰富的EMC公司专业人员,迅速的EMC设计审查是一个伟大的方式确认您的设计已经通过EMC测试的最佳机会。

不幸的是,大多数公司没有熟练的员工和电磁兼容工程师没有在房子知识创建一个EMC设计审查过程。EMC培训通常是令人难以置信的昂贵,与典型的定价(> 1500美元+短2 - 3天的研讨会费用/工程师。

我不能进入每一项覆盖全面EMC设计审查,但在这篇文章中我将详细的一些最重要的方面,我总是检查。下面的部分给你一个顶级的概述我如何为客户做EMC设计评审。

如何开始

定义您的通过/失败标准

没有明确定义的通过/失败标准,你没有一个好的规范。在某些情况下,你的产品可能只是对辐射和排放性能进行测试。在其他方面,你的产品也可能受到免疫ESD等现象,和EFT激增。第一个任务是对细节的限制和排放水平和免疫力,你的产品必须达到EMC测试期间。

排放限制

首先,你应该定义的排放限制你的产品。这些可能取决于环境,你的产品将用于和地区的世界,它将被出售。最重要的一个地方开始制定你的产品是否属于“甲级”或“B类”的限制。下面是FCC的区别:

类数码设备:数字设备销售用于商业、工业或商业环境、独家销售的设备供公众使用或打算在家里使用。

B类数字设备:数字设备销售中使用的居住环境尽管使用在商业,商业和工业环境。这类设备的例子包括,但不限于,个人电脑,计算器,和类似的电子设备销售供公众使用。

重要的是要注意,B类限制明显低于A类的限制。

限制也不同地理区域之间和产品类型之间。检查标准适用于你的产品(或问一个测试实验室)的限制,你需要满足。

我已经包括了一个例子下面的一些限制B类无意发射装置,这样您就可以看到它是什么样子。上下频率覆盖的范围取决于内部时钟频率出现在你的产品,同时也取决于标准,适用于你的产品。

虽然你可以领略到的辐射排放特定网设计中使用免费工具,像“最大排放计算器克莱姆森大学的工具,它不是非常实际使用这样的工具来分析一个完整的设计。排放限制通常覆盖辐射进行了排放以及以太网进行排放(如适用)。

发现排放限制适用于您的特定的产品给你一个好主意,这将是多么困难让你以下产品的排放限制。

免疫水平和通过/失败标准

如果免疫测试适用于你的产品(通常是强制性的CE标志和全球产品族标准),那么值得发现的测试水平EMC实验室使用,测试将被应用,如何你的产品需要执行期间和之后的测试(这就是所谓的性能标准)。这将会帮助你找出应用EMC压制设备,什么等级选择,也会给你一个想法的关心你需要多少。如果你有一个你使用常规的测试实验室,他们应该很乐意为您提供一个测试计划提前,这样您就可以使用它在设计阶段的产品开发周期。如果你有一个与测试实验室,他们应该愿意帮助你。如果他们不是,也许是时候开始寻找不同的测试实验室。

你可以看到的一个例子免疫测试计划,其中包括水平将适用于你的产品和你的产品需要满足的条件。

通过/失败标准的定义可以从标准到标准略有不同,但这是一个描述的性能标准的国际通用的免疫标准住宅,商业和轻工业环境(IEC 61000-6-1):

)性能标准:设备应按计划继续运营期间和之后的测试。没有性能退化或丧失功能是允许低于制造商规定的性能水平,当装置作为目的。性能水平可能被允许的性能损失所取代。如果最低性能水平或允许的性能损失不是由制造商指定的,这可能源于产品描述和文档和用户可能合理预期的设备如果使用。

b)性能标准b:设备应按计划继续运营后测试。没有性能退化或丧失功能是允许低于制造商规定的性能水平,当装置作为目的。性能水平可能被允许的性能损失所取代。在测试期间,降解性能却是允许的。没有变化的实际操作状态或存储的数据是被允许的。如果最低性能水平或允许的性能损失不是由制造商指定的,这可能源于产品描述和文档和用户可能合理预期的设备如果使用。

c)性能标准c:提供的功能是允许的,暂时的损失函数是self-recoverable还是可以恢复的操作控制。

要找到你的产品的性能标准必须满足测试实验室。

排放

1。选择正确的层叠

配置正确的PCB堆栈是EMC性能的基础。没有足够的层数为给定的复杂性和不正确的层序和使用,你会让你的工作进行的控制辐射和排放相当困难。如果你的老板将你减少层数到节省PCB成本,只要记住,通常有一个贸易与EMC性能,有可能损害公司的钱包。

良好的PCB堆栈的可取的特点(从EMC的角度来看)是:

•相邻信号层平面层

•信号层紧密耦合的返回电源/地平面

•权力和理由紧密耦合

•高速信号埋层

•对称

记住这些特性,下面是示例层堆栈4和6层板:

4层堆栈示例

在这个图中你可以看到两种不同的方法可以实现4层堆栈。看看你是否能工作从上面列出的可取的特点,每个堆栈的权衡。

6层示例堆栈

你能找出为什么左边堆栈不推荐?

我没有时间在这里,但是堆栈几何和PCB材料也可以严重影响EMC性能。那是因为它将定义网和飞机的阻抗层不等。董事会没有仔细考虑阻抗,可以运行在重要的信号完整性和电源交付网络(生产)的问题。

2。每一个集成电路有足够的分离吗?

这个是重复很多,但值得在EMC设计评审,验证和确认每一个集成电路拥有足够的解耦。做EMC设计为客户评论的时候,我通常找到至少两个ICs或压水式反应堆/接地销对设计师忘了添加分离帽或帽子已经实现的方式会使他们很无效。你可以看到下面增加解耦的影响IC(复制许可威廉姆森实验室)。

左上角图显示了分离对供给的影响噪声在频域和右上角图显示了在时间域的影响。可以看到,解耦帽时最优性能低于IC和路由之间尽可能直接压水式反应堆和接地针。

值得注意的是,去耦电容的重要特点不仅包括电容器的值(nF、酚醛等),但也ESR(等效串联电阻)和英语(等效串联电感)。这版的博客很好地解释在生产这些特征阻抗的影响。

3所示。检查在返回路径

如果你不熟悉返回路径,它只是意味着电流回源的路线。当你有一个集成电路,供应电流到另一个设备,目前有一个大小相等,方向相反,旅行回源设备。

上面的图表说明了直流的返回路径阻力最小的路径。交流(更高频率的信号)的返回路径电感最小的路径,通常在一个参考平面上直接在源信号。每当有削减在返回路径参考面,返回当前必须绕流降低电感最小的路径。这形成了一个不错的电流环,有潜力成为一个有效的散热器。

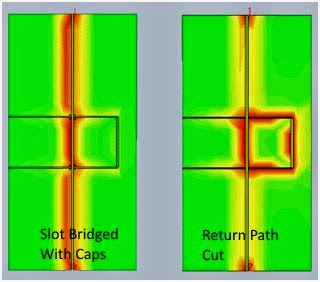

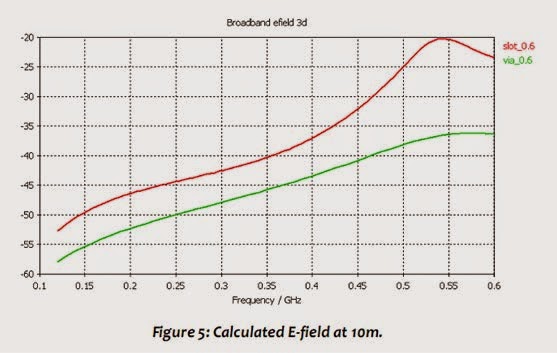

下面的图显示了一个0.5 GHz的信号,遍历地上飞机。右图中可以看出返回路径上的电流分布发现在插槽,因此使得一个循环。左边的图片展示了一个场景,削减在返回路径弥合了电容器允许高频返回当前“跳”的差距。

影响远场辐射排放这个信号可能会让你大吃一惊。这个场景的模拟表明,排放测量仅在10米从这个网可以超过30分贝更高的飞机返回。这无疑意味着通过或失败的区别在EMC实验室。

(来源未知)

在EMC设计审查,你应该查看布局2层一次,仔细确认你所有的数字信号一个定义良好的返回路径没有削减。如果减少返回路径是必要的任何理由,然后确保削减与电容器的低阻抗桥接在感兴趣的频率。

免疫力

1。ESD保护已经应用到所有外部端口?

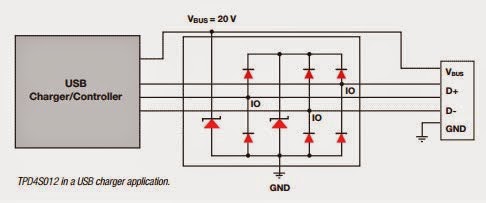

一旦你知道哪些端口将测试你的产品,你可以添加端口EMC设计评审清单。现在去确认每个港口都有足够的ESD保护电路板,在正确的地点和正确的评级。这是USB接口的一个例子,具有良好的防静电保护(从德州仪器)。

注意保护应该尽可能的身体接近端口连接器。许多不同类型的ESD保护装置是可用的。检查中的ESD部分”第一次正确EMC设计“电子书的更多细节。

密切相关这一项是验证净净许可和ESD注入点附近飞机许可不允许“弧”。这是为了确保委托人不能跳转到另一个导体和潜在的其他产品造成破坏。确保所需的建议许可弧不发生在各种情况下都包含在给定的电压水平ipc - 2221标准。

2。敏感的电路保护

辐射免疫是一种很常见的测试,适用于大多数电子设备运往欧洲,或者那些坚持国际产品标准。该领域的优势,你的产品可能受到不同1 V / m和200 V / m之间根据标准。领域也通常席卷频率80 MHz - 4 GHz(一些标准可能会比这更高和更低)。

如果你的产品包含敏感电路等模拟测量电路或射频电路,然后甚至低功率辐射电场可以引入重大问题。一个共同的和廉价的方式保护电路免受辐射领域是提供一个小盾感兴趣的电路。

一些简单的检查,我在EMC设计审查:

•有什么电路元素可能容易受到辐射电场?

•保护接地在多个点吗?

•PCB盾安装紧密吗?

•检查焊点不干燥

•是光阑(例如通风)盾最小化?

•如果需要光阑,他们是定位在最远的点远离敏感电路?

注意屏蔽独自常常是不够的你的敏感电路辐射电场进行免疫接种。字段通常由外部布线和耦合到电路板上。一旦能量的电路板,它会影响敏感电路的电压波动在地面上或飞机。EMC设计审查Pro软件进入更深度有关辐射免疫力,涵盖物品,如带宽限制,敏感网络因素和内部布线等等。

安迪收购方

注意:这篇文章是编辑和复制的许可EMC FastPass。EMC FastPass帮助制造商进入市场更便宜、更快的EMC /射频设计审查软件和在线视频培训课程。